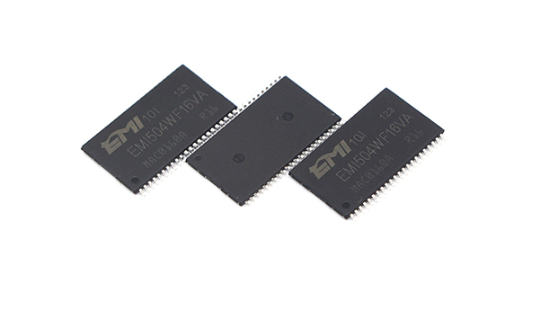

First,overview of EMI high-speed asynchronous Async SRAM

SRAM(Static Random Access Memory)usually exchanges data with a data 8bit width of 8 bits or 16 bits.In terms of performance parameters,the typical access time of mainstream asynchronous SRAM can reach 10ns level,and the power supply voltage covers various specifications such as 1.8V,3.3V and 5V to adapt to embedded scenes with different power consumption requirements.At present,the maximum capacity commonly used in the industry can reach 32Mb,and some high-end models also integrate ECC check function to ensure data reliability,and support burst mode to improve data transmission efficiency.

Asynchronous SRAM(Async SRAM)is a kind of traditional memory type with strong vitality.Its most notable feature is that its operation is completely independent of the external clock of the computer or processor system.This"self-sufficient"working mode makes it show high stability and signal integrity in specific fields,especially in the application of Level 2 Cache.

When the system needs to read data,the controller only needs to provide a stable address signal and pull down the chip selection and output enable.The combinational logic circuit in asynchronous SRAM will immediately respond to the address change,and after a fixed access time(such as 10ns),the data will appear on the data bus stably.This working mode brings a significant advantage:extremely low access delay.Because there is no clock synchronization link,there is no latency caused by waiting for clock alignment.This is a very valuable feature for the second-level cache that needs fast random access and the EMI environment that needs to deal with sudden irregular signals.

Second,the architecture principle of EMI high-speed asynchronous Async SRAM

1.6T storage unit

The core memory cell of Async SRAM adopts the classic 6-transistor(6T)structure.These six transistors are carefully wired to form a pair of cross-coupled inverters to form a bistable latch circuit.

EMI high-speed asynchronous Async SRAM working mechanism:this latch circuit is similar to an electronic seesaw.As long as the power supply is maintained,it can be kept in a"0"or"1"state indefinitely,and it is not necessary to maintain data by refreshing the capacitor like DRAM.

Performance cost of EMI high-speed asynchronous Async SRAM:the price of this high speed and high stability is low integration.Compared with a DRAM cell that only needs one transistor and one capacitor,the 6T structure occupies a larger chip area,which directly leads to the SRAM cost being much higher than that of DRAM.

2.Two-dimensional array and address decoding

In order to organize these massive 6T cells efficiently,a two-dimensional array architecture is adopted in asynchronous SRAM.

Addressing logic:When the external controller of EMI high-speed asynchronous Async SRAM initiates an access request,the address signal is simultaneously sent to the row address decoder and the column address decoder.For example,in a 64×8 SRAM architecture,the row decoder is responsible for translating the 6-bit address into one of 64 Word Line and selecting a specific row;Subsequently,the column decoder accurately locates the specific memory cell through the column select line.

Data flow:once the intersection of rows and columns is locked,the data in the storage unit will be amplified by the sense amplifier and output through the I/O buffer.The whole reading and writing process is completely coordinated by the on-chip control logic,and each step of operation is directly triggered by external input reading and writing instructions(such as chip select signal CE and write enable signal WE),without waiting for the next clock edge.

Third,why recommend EMI high-speed asynchronous Async SRAM

The EMI high-speed Async SRAM asynchronous interface of Yingshang Microelectronics Agency has stronger tolerance for glitches and noises on input signals.As long as the address and control signal meet the setup and hold time,the device can work reliably,which makes it perform well in industrial control or automotive electronic applications with large power noise.In the system design,Yingshang's asynchronous SRAM provides a similar"plug and play"experience.Engineers don't need to adjust the clock phase and delay locked loop(DLL)settings repeatedly like configuring synchronous SRAM,thus reducing the complexity of hardware debugging.If you have any demand for Async SRAM products,please contact Yingshangwei.

Shenzhen Ramsun Microelectronics Co.,Ltd(Ramsun International) is a vendor of the seimicondutor componets and the memory IC’s solution with clear market advantage. We still focus on the promotion for some famous semicondutor brand ,and specially take the RAM(Random Access Memory) as our core products.

We are the authorized agent as designated by NETSOL、JSC、EVERSPIN、NETSOL、VTI、IPSiLog and Sinochip.And Lyontek.so on.