SRAM的结构框图解

2020-02-24 10:46:19

SRAM 即静态RAM.它也由晶体管组成,SRAM的高速和静态特性使它们通常被用来作为Cache存储器。计算机的主板上都有Cache插座。

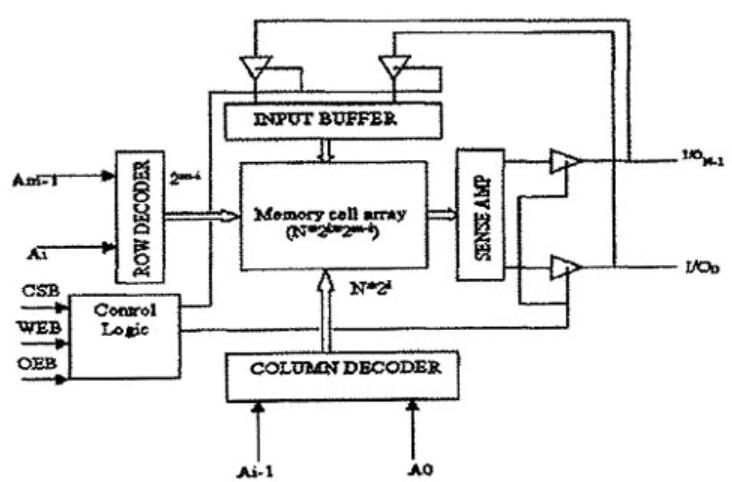

下图所示的是一个

SRAM的结构框图。

由上图看出SRAM一般由五大部分组成,即存储单元阵列、地址译码器(包括行译码器和列译码器)、灵敏放火器、控制电路和缓冲/驱动电路。在图中A0-Am-1为地址输入端,CSB. WEB和OEB为控制端,控制读写操作,为低电平有效1100-11ON-1为数据输入输出端。存储阵列中的每个存储单元都与其它单元在行和列上共享电学连接,其中水平方向的连线称为“字线”,而垂直方向的数据流入和流出存储单元的连线称为“位线”。

通过输入的地址可选择特定的字线和位线,字线和位线的交叉处就是被选中的存储单元,每一个存储单元都是按这种方法被唯一选中,然后再对其进行读写操作。有的存储器设计成多位数据如4位或8位等同时输入和输出,这样的话就会同时有4个或8个存储单元按上述方法被选中进行读写操作。

在SRAM 中,排成矩阵形式的存储单元阵列的周围是译码器和与外部信号的接口电路。存储单元阵列通常采用正方形或矩阵的形式,以减少整个芯片面积并有利于数据的存取。以一个存储容量为4K位的SRAM为例,共需12条地址线来保证每一个存储单元都能被选中(212 =-4096)。如果存储单元阵列被排列成只包含一列的长条形,则需要一个12/4K位的译码器,但如果排列成包含64行和64列的正方形,这时则只需一个6/64位的行译码器和一个6/64位的列译码器,行、列译码器可分别排列在存储单元阵列的两边,64行和64列共有4096个交叉点,每一个点就对应一个存储位。

因此将存储单元排列成正方形比排列成一列的长条形要大大地减少整个芯片地面积。存储单元排列成长条形除了形状奇异和面积大以外,还有一个缺点就是排在列的上部的存储单元与数据输入/输出端的连线就会变得很长,特别是对于容量比较大得存储器来说,情况就更为严重,而连线的延迟至少是与它的长度成线性关系,连线越长,线上的延迟就越大,所以就会导致读写速度的降低和不同存储单元连线延迟的不一致性,这些都是在设计中需要避免的。

本文关键词: SRAM

上一篇文章:静态随机存储器SRAM存储数据原理

深圳市英尚微电子有限公司是一家专业的静态随机记忆体产品及方案提供商,十年来专业致力代理分销存储芯片IC, SRAM、MRAM、pSRAM、 FLASH芯片、SDRAM(DDR1/DDR2/DDR3)等,为客人提供性价比更高的产品及方案。

英尚微电子中国区指定的授权代理:VTI代理、NETSOL、JSC济州半导体(EMLSI)、Everspin 、IPSILOG、LYONTEK、ISSI、CYPRESS、ISOCOME、PARAGON、SINOCHIP、UNIIC; 著名半导体品牌的专业分销商 如:RAMTROM、ETRON、FUJITSU、LYONTEK、WILLSEMI。

更多资讯关注SRAMSUN. www.sramsun.com 0755-66658299