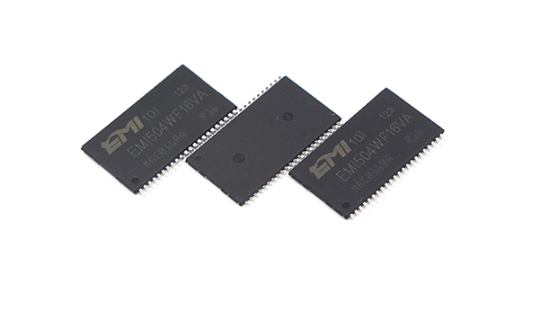

推荐EMI高速异步Async SRAM

2026-03-12 10:36:52

一、EMI高速异步Async SRAM概述

SRAM(静态随机存取存储器)通常以8bit或16bit的数据位宽进行数据交换。在性能参数上,主流的异步SRAM典型访问时间可达10ns级别,供电电压则覆盖1.8V、3.3V及5V等多种规格,以适应不同功耗要求的嵌入式场景。目前业界常用的最大容量可达32Mb,部分高端型号还集成了ECC校验功能以保障数据可靠性,并支持突发模式以提高数据传输效率。

异步SRAM(Async SRAM)是一种较为传统但生命力极强的存储器类型。它最显著的特征在于其运作完全独立于计算机或处理器系统的外部时钟。这种“自给自足”的工作方式,使其在特定领域,尤其是作为二级缓存(Level 2 Cache)的应用中,展现出了极高的稳定性和信号完整性。

当系统需要读取数据时,控制器只需提供稳定的地址信号并拉低片选和输出使能。异步SRAM内部的组合逻辑电路会立即对地址变化做出反应,经过一个固定的访问时间(如10ns)后,数据便稳定出现在数据总线上。这种工作模式带来一个显著优势:极低的访问延迟。因为没有时钟同步环节,也就没有了等待时钟对齐所造成的潜伏期。这对于需要快速随机访问的二级缓存以及需要处理突发不规则信号的EMI环境而言,是非常宝贵的特性。

二、EMI高速异步Async SRAM的架构原理

1.6T存储单元

Async SRAM的核心存储单元采用经典的6晶体管(6T)结构。这六个晶体管通过精心布线,构成了一对交叉耦合的反相器,形成一个双稳态锁存电路。

EMI高速异步Async SRAM工作机制:这种锁存电路类似于一个电子跷跷板,只要维持供电,它就能无期限地稳定保持在“0”或“1”的状态,无需像DRAM那样通过刷新电容来维持数据。

EMI高速异步Async SRAM性能代价:这种高速度和高稳定性的代价是集成度较低。相比仅需一个晶体管和一个电容的DRAM单元,6T结构占用更大的芯片面积,这也直接导致了SRAM成本远高于DRAM。

2.二维阵列与地址解码

为了高效组织这些海量的6T单元,异步SRAM内部采用了二维阵列架构。

寻址逻辑:当EMI高速异步Async SRAM外部控制器发起访问请求时,地址信号被同时送入行地址解码器和列地址解码器。例如,在一个64×8容量的SRAM架构中,行解码器负责将6位地址翻译成64条字线(Word Line)中的一条,选中特定的行;随后,列解码器通过列选择线(Bit Line)精确定位到具体的存储单元。

数据流动:一旦行列交叉点被锁定,该存储单元中的数据便会通过灵敏放大器放大,并经由I/O缓冲器输出。整个读写过程完全由片内的控制逻辑协调,每一步操作都由外部输入的读写指令(如片选信号CE、写使能信号WE)直接触发,无需等待下一个时钟边沿。

三、为何在推荐EMI高速异步Async SRAM

英尚微电子代理的EMI高速Async SRAM异步接口对输入信号上的毛刺和噪声具有更强的容忍度。只要地址和控制信号满足建立保持时间,器件就能可靠工作,这使得它在电源噪声较大的工业控制或汽车电子应用中表现优异。在系统设计中,英尚的异步SRAM提供了类似“即插即用”的体验。工程师无需像配置同步SRAM那样反复调整时钟相位和延迟锁定环(DLL)设置,从而降低了硬件调试的复杂度。如果您有Async SRAM产品的需求,请联系英尚微。

本文关键词:Async SRAM

上一篇文章:推荐EMI高速异步Async SRAM

深圳市英尚微电子有限公司是一家专业的静态随机记忆体产品及方案提供商,十年来专业致力代理分销存储芯片IC, SRAM、MRAM、pSRAM、 FLASH芯片、SDRAM(DDR1/DDR2/DDR3)等,为客人提供性价比更高的产品及方案。

英尚微电子中国区指定的授权代理:VTI、NETSOL、JSC济州半导体(EMLSI)、Everspin 、IPSILOG、LYONTEK、ISSI、CYPRESS、ISOCOME、PARAGON、SINOCHIP、UNIIC