SRAM随机存储器的特点及结构

2020-04-28 09:20:30

随着微电子技术的迅猛发展,

SRAM存储器逐渐呈现出高集成度、快速及低功耗的发展趋势。在半导体存储器的发展中,静态存储器(SRAM)由于其广泛的应用成为其中不可或缺的重要一员。下面由英尚微电子详细介绍关于SRAM随机存储器的特点及结构。

SRAM随机存储器的特点

随机存储器最大的特点就是可以随时对它进行读写操作,但当电源断开时,存储信息便会消失。随机存储器依照数据存储方式的不同,主要可以分为动态随机存储器(DRAM)与静态随机存储器(SRAM)两大类。DRAM 以电容上存储电荷数的多少来代表所存储的数据,电路结构十分简单(采用单管单电容1T-1C的电路形式),因此集成度很高,但是因为电容上的电荷会泄漏,为了能长期保存数据,它需要定期的刷新操作。这不但使DRAM 的读写控制变得复杂,而且也降低了它的读写速度。DRAM 主要用作主存储器。SRAM 是依靠一对反相器以闭环形式连接的存储电路,它的代码的读出是非破坏性的,并不需要相应的刷新电路,因此它的存取速度比DRAM 要快。但是,SRAM 需要用更多的晶体管来存储一位的信息(采用六管单元或四管两电阻单元储存一位数据),因而其位密度比其它类型的低,造价也高。静态存储器多用于二级高速缓存。

SRAM随机存储器的结构

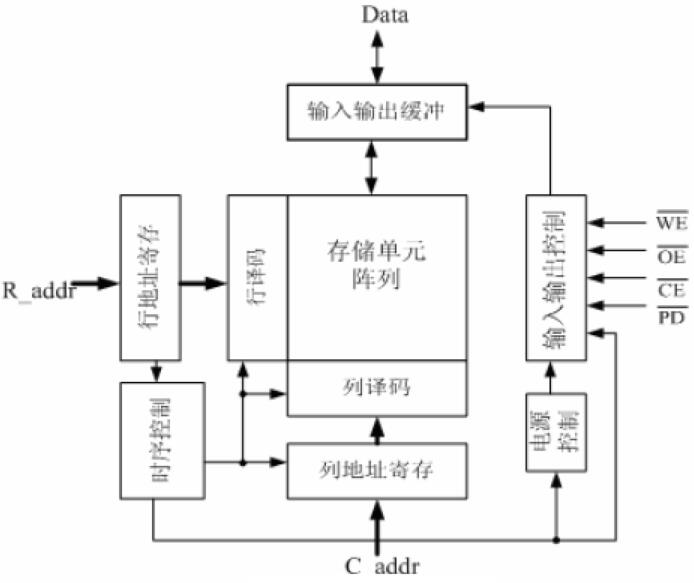

图2.1 给出了SRAM的一般结构[1],主要包括存储阵列、译码器、时序控制、输入输出缓冲、输入输出控制等。存储阵列由存储单元构成,用于保存数据,存储阵列的布局对整个存储器的面积、功耗、可靠性等有着非常重要的影响;由于存储阵列是按行、列分开组织的,因此,译码器也分为行译码器和列译码器,并且地址译码之前,需要对地址进行缓存;输入输出缓冲是存储阵列与外部数据交换的接口,用于放大存储单元读出的信号,以及将输入信号写入到存储阵列之中;输入输出控制模块根据控制信号的时序要求,控制存储器的读出、写入等操作;电源控制是一个可选的电路单元,主要是为了低功耗的要求,当整个存储器不需要进行读写操作时,通过电源控制可以控制内部无效的翻转操作,从而节省功耗。完整的存储结构中可能还包括测试电路模块,例如内部监测电路、BIST电路等等。

图1.1 SRAM 结构

图1.2 存储器的功能模型 图1.3 存储器的关键路径

图1.2 是SRAM的功能模型,图1.3 给出了SRAM的关键路径,也就是从地址输入开始到数据输出之间影响读出操作的通路。为了更好地理解SRAM的关键路径,首先对SRAM的读写过程进行初步的分析。以读出操作为例,首先是读信号和地址信号有效,然后在内部时序电路的控制下,对存储阵列中的位线进行预充电,接下来行、列译码器输出,选中相应的存储单元的字线和位线,数据经灵敏放大器后到输出缓冲器中,就完成了读出操作的全过程。显然图1.3 的关键路径就充分反映了这个过程。

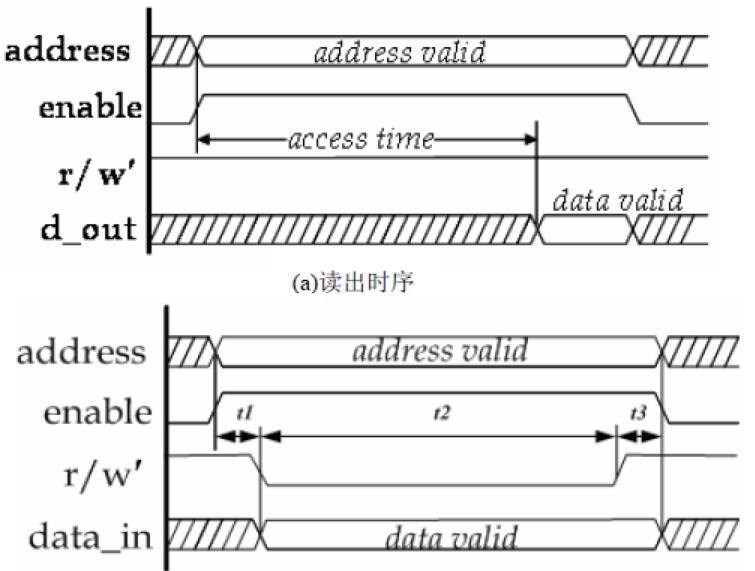

图1.4 给出了

SRAM存储器的读写时序。在读出操作中,访问时间(access time)就是指从地址有效算起,到有效数据输出的时间;图1.4 (b)中t1 是从地址和使能信号稳定到写信号有效所需的最小时间,t2 是写信号无效之前必须保持的最小时间,t3是写信号无效之后地址信号仍需保持的最小时间。t1、t2、t3 相加就是一个写周期时间。

图1.4 存储器的读写时序

以上对

VTI代理英尚微电子对SRAM的结构、操作进行了简单地介绍和分析。

本文关键词: SRAM SRAM随机存储器

相关文章:静态随机存储器SRAM存储数据原理

深圳市英尚微电子有限公司是一家专业的静态随机记忆体产品及方案提供商,十年来专业致力代理分销存储芯片IC, SRAM、MRAM、pSRAM、 FLASH芯片、SDRAM(DDR1/DDR2/DDR3)等,为客人提供性价比更高的产品及方案。

英尚微电子中国区指定的授权代理:VTI代理、NETSOL、JSC济州半导体(EMLSI)、Everspin 、IPSILOG、LYONTEK、ISSI、CYPRESS、ISOCOME、PARAGON、SINOCHIP、UNIIC; 著名半导体品牌的专业分销商 如:RAMTROM、ETRON、FUJITSU、LYONTEK、WILLSEMI。

更多资讯关注SRAMSUN. www.sramsun.com 0755-66658299